Storage System- Device to System Perspective

Course | Master of Science in Electrical Engineering

Semester: Spring 2025

Instructor: Dr. Biswajit Ray

Course Overview

Technical Scope

Final Reflection

Memory Cell Design:

Gained a solid understanding of floating-gate memory cells as well as SRAM and DRAM structures, focusing on the underlying device physics and operational principles.SRAM & DRAM Reliability:

Explored key reliability challenges specific to SRAM and DRAM, including soft errors, access latency, and sensitivity to environmental conditions like temperature and radiation.Storage Array Architecture:

Studied 2D and 3D NAND Flash architectures alongside SRAM and DRAM arrays, analyzing trade-offs in density, performance, and reliability.Reliability Analysis:

Investigated critical failure mechanisms such as endurance degradation, retention loss, noise, and environmental effects across multiple memory types.Error Management & Optimization:

Applied techniques like ECC (Error Correction Codes), wear-leveling, and redundancy to maintain system integrity and extend memory lifespan.Security & Data Integrity:

Evaluated vulnerabilities in storage systems and implemented countermeasures for secure data handling, including data sanitization and protection against emerging threats.Design Trade-offs:

Formulated and applied algorithms to balance trade-offs in performance, power, and area across diverse storage technologies and system requirements.

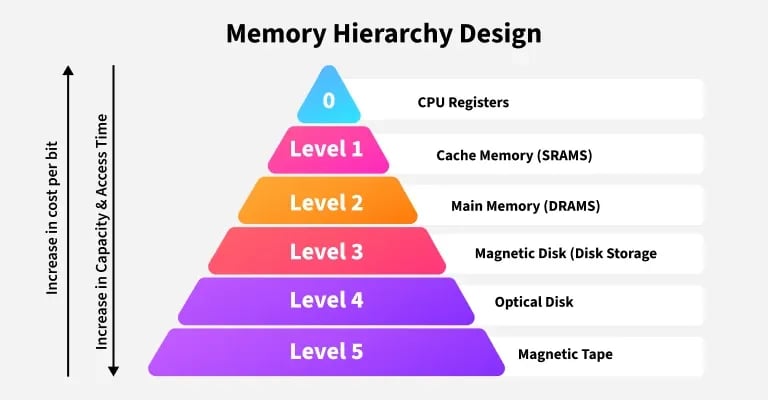

This course explored modern storage system design from the ground up, starting with the physics of memory cells and advancing to system-level solutions for reliability and security. Adopting a bottom-up approach, it bridged low-level device understanding with high-level architectural strategies, focusing on both the technical challenges and the design trade-offs inherent in today’s storage technologies. It covered everything from the design and reliability of floating-gate memory cells to the architecture of complex storage systems like NAND Flash. Key emphasis was placed on evaluating real-world reliability concerns—such as endurance, retention loss, and radiation effects.

Project : Scaling effects on SRAM Data Retention Voltage

SRAM leakage during standby mode can dominate total system power consumption, threatening battery life and operational efficiency in battery-powered systems. A promising technique to mitigate this is reducing the standby supply voltage (VDD) to the lowest possible value at which data is still retained — known as the Data Retention Voltage (DRV). Understanding the limits of DRV and its dependencies on process variations, temperature, and transistor sizing is vital.

This course provided a strong foundation in modern storage system design, covering SRAM, DRAM, and Flash memory technologies. I gained practical insight into memory cell design, reliability issues like endurance and retention, and the impact of environmental conditions. Through applied problem solving, I explored performance, power, and area trade-offs, and implemented techniques such as error correction and wear-leveling. The course also emphasized system-level security, equipping me with the skills to design storage solutions that are both efficient and resilient—key capabilities for roles in hardware design, embedded systems, and memory architecture.

Connect

Explore my projects and coursework for insights.

afiah468@gmail.com

+970-689-1697

© 2025. All rights reserved.